,輸出對(duì)應(yīng)頻率的周期信號(hào)

Feedback Loop反饋回路

4. 通過PLL,如何把KOAN晶振4MHz的基準(zhǔn)頻率倍頻到40MHz ?

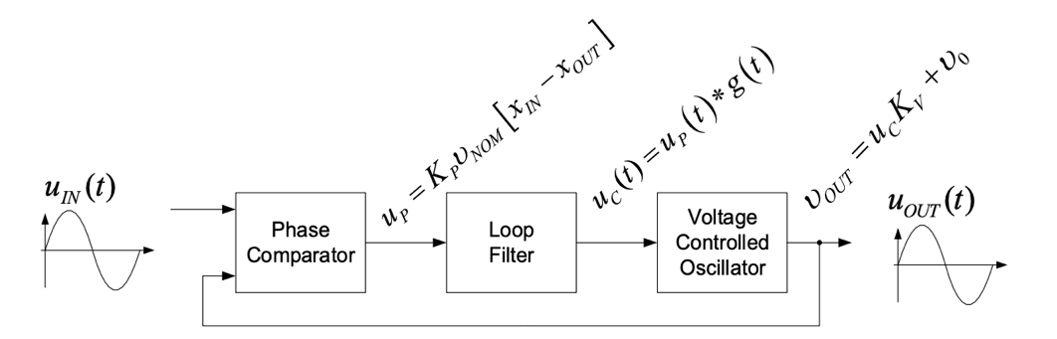

假設(shè)VCO先產(chǎn)生一個(gè)大概35MHz的頻率,經(jīng)過10倍分頻后得到3.5MHz 。VCO的輸出通過反饋回路輸入到相位比較器

。比較得知3.5MHz小于4MHz

,相位比較器輸出一個(gè)電壓(誤差電壓)

。在經(jīng)過濾波后,得到VCO的控制電壓

。

鎖相環(huán)提高到38MHz。經(jīng)過對(duì)比后,依然不足4M(>3.8MHz)。再不斷通過負(fù)反饋處理

,最終得到穩(wěn)定的精度的時(shí)鐘頻率

。

5. 如果同時(shí)需要50M和100M,系統(tǒng)時(shí)鐘選擇50M還是100M?

采用100MHz晶振。

因?yàn)榉诸l的時(shí)鐘比倍頻的時(shí)鐘質(zhì)量好,穩(wěn)定性高。分頻的電路比較簡(jiǎn)單。相比之下

,倍頻電路比較復(fù)雜

,需要相位比較器

,回路濾波器

,壓控振蕩器

,分頻器等。

發(fā)布時(shí)間:2022-02-17

發(fā)布時(shí)間:2022-02-17  閱讀次數(shù):1186次

閱讀次數(shù):1186次